TMS320C6748EZWTD4 IC DSP FIX/FLOAT POINT 361NFBGA

Parameter izdelka

Opis

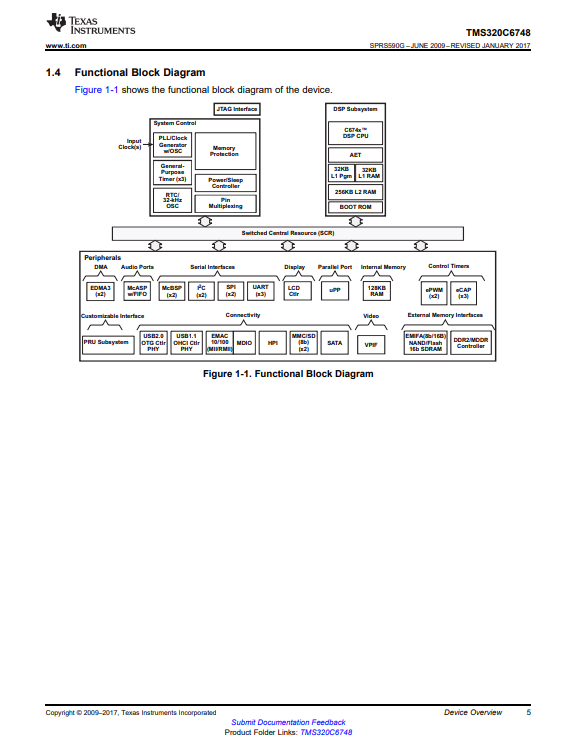

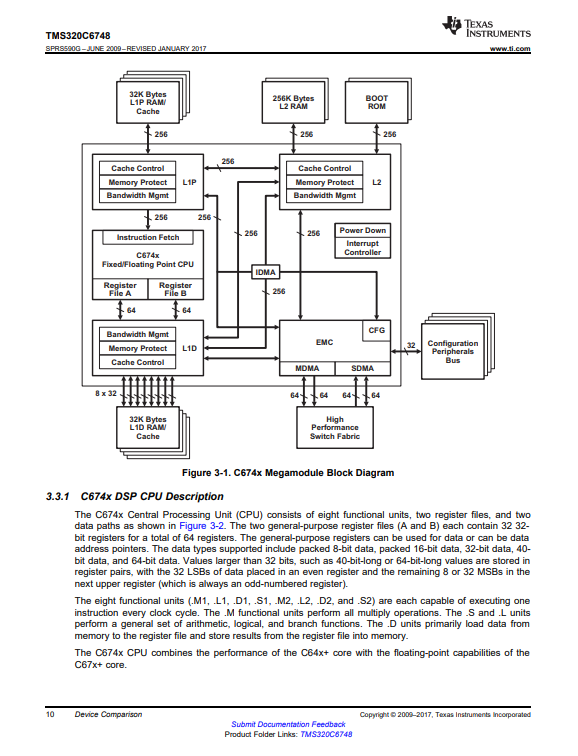

DSP s fiksno in plavajočo vejico TMS320C6748 je aplikacijski procesor z nizko porabo energije, ki temelji na jedru C674x DSP.Ta DSP zagotavlja znatno nižjo moč kot drugi člani platforme TMS320C6000™ DSP-jev.Naprava omogoča proizvajalcem originalne opreme (OEM) in proizvajalcem originalne zasnove (ODM), da na trg hitro predstavijo naprave z robustnimi operacijskimi sistemi, bogatimi uporabniškimi vmesniki in visoko zmogljivostjo procesorja z največjo prilagodljivostjo popolnoma integrirane mešane procesorske rešitve.Jedro DSP naprave uporablja dvonivojsko arhitekturo, ki temelji na predpomnilniku.Programski predpomnilnik 1. stopnje (L1P) je 32-KB neposredno preslikan predpomnilnik, podatkovni predpomnilnik 1. stopnje (L1D) pa je 32-KB dvosmerni, nastavljeno-asociativni predpomnilnik.Programski predpomnilnik ravni 2 (L2P) je sestavljen iz 256 KB pomnilniškega prostora, ki si ga delita programski in podatkovni prostor.Pomnilnik L2 je mogoče konfigurirati kot preslikani pomnilnik, predpomnilnik ali kombinacijo obeh.Čeprav je DSP L2 dostopen drugim gostiteljem v sistemu, je dodatnih 128 KB skupnega pomnilnika RAM na voljo za uporabo drugim gostiteljem, ne da bi to vplivalo na zmogljivost DSP.Za naprave z omogočeno varnostjo TI-jev Basic Secure Boot uporabnikom omogoča zaščito lastniške intelektualne lastnine in zunanjim subjektom preprečuje spreminjanje algoritmov, ki jih razvijejo uporabniki.Z zagonom od »korena zaupanja«, ki temelji na strojni opremi, varni zagonski tok zagotavlja znano dobro izhodišče za izvajanje kode. Vrata JTAG so privzeto zaklenjena, da preprečijo napade emulacije in odpravljanja napak; vendar pa je vrata JTAG mogoče omogočeno med postopkom varnega zagona med razvojem aplikacije. Zagonski moduli so šifrirani, medtem ko sedijo v zunanjem obstojnem pomnilniku, kot je flash ali EEPROM, in so dešifrirani in overjeni, ko se naložijo med varnim zagonom. Šifriranje in dešifriranje ščiti IP strank in jim omogoča varno nastavite sistem in začnite delovati naprave z znano, zaupanja vredno kodo. Osnovni varni zagon uporablja SHA-1 ali SHA-256 in AES-128 za preverjanje veljavnosti zagonske slike. Osnovni varni zagon uporablja tudi AES-128 za šifriranje zagonske slike. Varen potek zagona uporablja večplastno šifrirno shemo, ki ne le ščiti zagonski proces, ampak ponuja tudi možnost varne nadgradnje zagonske in aplikacijske programske kode.samo za napravo in ustvarjen z uporabo generatorja naključnih števil s certifikatom NIST-800-22, se uporablja za zaščito šifrirnih ključev strank.Ko je potrebna posodobitev, stranka uporabi šifrirne ključe za ustvarjanje nove šifrirane slike.

| Specifikacije: | |

| Atribut | Vrednost |

| Kategorija | Integrirana vezja (IC) |

| Vgrajeno - DSP (procesorji digitalnih signalov) | |

| Proizvajalec | Texas Instruments |

| serija | TMS320C674x |

| Paket | Pladenj |

| Status dela | Aktiven |

| Vrsta | Fiksna/plavajoča vejica |

| Vmesnik | EBI/EMI, Ethernet MAC, gostiteljski vmesnik, I²C, McASP, SPI, UART, USB |

| Stopnja ure | 456MHz |

| Nehlapni pomnilnik | Zunanji |

| RAM na čipu | 448 kB |

| Napetost - I/O | 1,8 V, 3,3 V |

| Napetost - jedro | 1,30 V |

| delovna temperatura | -40°C ~ 90°C (TJ) |

| Vrsta namestitve | Površinska montaža |

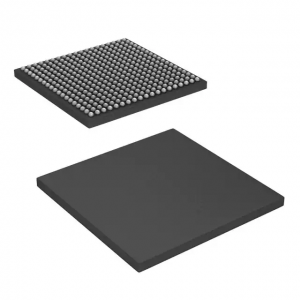

| Paket/kovček | 361-LFBGA |

| Paket naprave dobavitelja | 361-NFBGA (16x16) |

| Osnovna številka izdelka | TMS320 |

PovezanoIZDELKI

-

Tel

-

E-naslov

-

skype

-

WhatsApp

WhatsApp